VHDL Logical Operators and Signal Assignments for Combinational Logic

In this post, we discuss the VHDL logical operators, when-else statements , with-select statements and instantiation . These basic techniques allow us to model simple digital circuits.

In a previous post in this series, we looked at the way we use the VHDL entity, architecture and library keywords. These are important concepts which provide structure to our code and allow us to define the inputs and outputs of a component.

However, we can't do anything more than define inputs and outputs using this technique. In order to model digital circuits in VHDL, we need to take a closer look at the syntax of the language.

There are two main classes of digital circuit we can model in VHDL – combinational and sequential .

Combinational logic is the simplest of the two, consisting primarily of basic logic gates , such as ANDs, ORs and NOTs. When the circuit input changes, the output changes almost immediately (there is a small delay as signals propagate through the circuit).

Sequential circuits use a clock and require storage elements such as flip flops . As a result, changes in the output are synchronised to the circuit clock and are not immediate. We talk more specifically about modelling combinational logic in this post, whilst sequential logic is discussed in the next post.

Combinational Logic

The simplest elements to model in VHDL are the basic logic gates – AND, OR, NOR, NAND, NOT and XOR.

Each of these type of gates has a corresponding operator which implements their functionality. Collectively, these are known as logical operators in VHDL.

To demonstrate this concept, let us consider a simple two input AND gate such as that shown below.

The VHDL code shown below uses one of the logical operators to implement this basic circuit.

Although this code is simple, there are a couple of important concepts to consider. The first of these is the VHDL assignment operator (<=) which must be used for all signals. This is roughly equivalent to the = operator in most other programming languages.

In addition to signals, we can also define variables which we use inside of processes. In this case, we would have to use a different assignment operator (:=).

It is not important to understand variables in any detail to model combinational logic but we talk about them in the post on the VHDL process block .

The type of signal used is another important consideration. We talked about the most basic and common VHDL data types in a previous post.

As they represent some quantity or number, types such as real, time or integer are known as scalar types. We can't use the VHDL logical operators with these types and we most commonly use them with std_logic or std_logic_vectors.

Despite these considerations, this code example demonstrates how simple it is to model basic logic gates.

We can change the functionality of this circuit by replacing the AND operator with one of the other VHDL logical operators.

As an example, the VHDL code below models a three input XOR gate.

The NOT operator is slightly different to the other VHDL logical operators as it only has one input. The code snippet below shows the basic syntax for a NOT gate.

- Mixing VHDL Logical Operators

Combinational logic circuits almost always feature more than one type of gate. As a result of this, VHDL allows us to mix logical operators in order to create models of more complex circuits.

To demonstrate this concept, let’s consider a circuit featuring an AND gate and an OR gate. The circuit diagram below shows this circuit.

The code below shows the implementation of this circuit using VHDL.

This code should be easy to understand as it makes use of the logical operators we have already talked about. However, it is important to use brackets when modelling circuits with multiple logic gates, as shown in the above example. Not only does this ensure that the design works as intended, it also makes the intention of the code easier to understand.

- Reduction Functions

We can also use the logical operators on vector types in order to reduce them to a single bit. This is a useful feature as we can determine when all the bits in a vector are either 1 or 0.

We commonly do this for counters where we may want to know when the count reaches its maximum or minimum value.

The logical reduction functions were only introduced in VHDL-2008. Therefore, we can not use the logical operators to reduce vector types to a single bit when working with earlier standards.

The code snippet below shows the most common use cases for the VHDL reduction functions.

Mulitplexors in VHDL

In addition to logic gates, we often use multiplexors (mux for short) in combinational digital circuits. In VHDL, there are two different concurrent statements which we can use to model a mux.

The VHDL with select statement, also commonly referred to as selected signal assignment, is one of these constructs.

The other method we can use to concurrently model a mux is the VHDL when else statement.

In addition to this, we can also use a case statement to model a mux in VHDL . However, we talk about this in more detail in a later post as this method also requires us to have an understanding of the VHDL process block .

Let's look at the VHDL concurrent statements we can use to model a mux in more detail.

VHDL With Select Statement

When we use the with select statement in a VHDL design, we can assign different values to a signal based on the value of some other signal in our design.

The with select statement is probably the most intuitive way of modelling a mux in VHDL.

The code snippet below shows the basic syntax for the with select statement in VHDL.

When we use the VHDL with select statement, the <mux_out> field is assigned data based on the value of the <address> field.

When the <address> field is equal to <address1> then the <mux_out> signal is assigned to <a>, for example.

We use the the others clause at the end of the statement to capture instance when the address is a value other than those explicitly listed.

We can exclude the others clause if we explicitly list all of the possible input combinations.

- With Select Mux Example

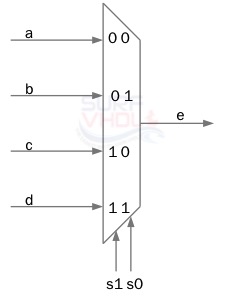

Let’s consider a simple four to one multiplexer to give a practical example of the with select statement. The output Q is set to one of the four inputs (A,B, C or D) depending on the value of the addr input signal.

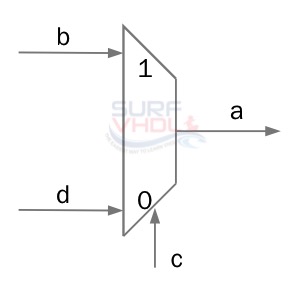

The circuit diagram below shows this circuit.

This circuit is simple to implement using the VHDL with select statement, as shown in the code snippet below.

VHDL When Else Statements

We use the when statement in VHDL to assign different values to a signal based on boolean expressions .

In this case, we actually write a different expression for each of the values which could be assigned to a signal. When one of these conditions evaluates as true, the signal is assigned the value associated with this condition.

The code snippet below shows the basic syntax for the VHDL when else statement.

When we use the when else statement in VHDL, the boolean expression is written after the when keyword. If this condition evaluates as true, then the <mux_out> field is assigned to the value stated before the relevant when keyword.

For example, if the <address> field in the above example is equal to <address1> then the value of <a> is assigned to <mux_out>.

When this condition evaluates as false, the next condition in the sequence is evaluated.

We use the else keyword to separate the different conditions and assignments in our code.

The final else statement captures the instances when the address is a value other than those explicitly listed. We only use this if we haven't explicitly listed all possible combinations of the <address> field.

- When Else Mux Example

Let’s consider the simple four to one multiplexer again in order to give a practical example of the when else statement in VHDL. The output Q is set to one of the four inputs (A,B, C or D) based on the value of the addr signal. This is exactly the same as the previous example we used for the with select statement.

The VHDL code shown below implements this circuit using the when else statement.

- Comparison of Mux Modelling Techniques in VHDL

When we write VHDL code, the with select and when else statements perform the same function. In addition, we will get the same synthesis results from both statements in almost all cases.

In a purely technical sense, there is no major advantage to using one over the other. The choice of which one to use is often a purely stylistic choice.

When we use the with select statement, we can only use a single signal to determine which data will get assigned.

This is in contrast to the when else statements which can also include logical descriptors.

This means we can often write more succinct VHDL code by using the when else statement. This is especially true when we need to use a logic circuit to drive the address bits.

Let's consider the circuit shown below as an example.

To model this using a using a with select statement in VHDL, we would need to write code which specifically models the AND gate.

We must then include the output of this code in the with select statement which models the multiplexer.

The code snippet below shows this implementation.

Although this code would function as needed, using a when else statement would give us more succinct code. Whilst this will have no impact on the way the device works, it is good practice to write clear code. This help to make the design more maintainable for anyone who has to modify it in the future.

The VHDL code snippet below shows the same circuit implemented with a when else statement.

Instantiating Components in VHDL

Up until this point, we have shown how we can use the VHDL language to describe the behavior of circuits.

However, we can also connect a number of previously defined VHDL entity architecture pairs in order to build a more complex circuit.

This is similar to connecting electronic components in a physical circuit.

There are two methods we can use for this in VHDL – component instantiation and direct entity instantiation .

- VHDL Component Instantiation

When using component instantiation in VHDL, we must define a component before it is used.

We can either do this before the main code, in the same way we would declare a signal, or in a separate package.

VHDL packages are similar to headers or libraries in other programming languages and we discuss these in a later post.

When writing VHDL, we declare a component using the syntax shown below. The component name and the ports must match the names in the original entity.

After declaring our component, we can instantiate it within an architecture using the syntax shown below. The <instance_name> must be unique for every instantiation within an architecture.

In VHDL, we use a port map to connect the ports of our component to signals in our architecture.

The signals which we use in our VHDL port map, such as <signal_name1> in the example above, must be declared before they can be used.

As VHDL is a strongly typed language, the signals we use in the port map must also match the type of the port they connect to.

When we write VHDL code, we may also wish to leave some ports unconnected.

For example, we may have a component which models the behaviour of a JK flip flop . However, we only need to use the inverted output in our design meaning. Therefore, we do not want to connect the non-inverted output to a signal in our architecture.

We can use the open keyword to indicate that we don't make a connection to one of the ports.

However, we can only use the open VHDL keyword for outputs.

If we attempt to leave inputs to our components open, our VHDL compiler will raise an error.

- VHDL Direct Entity Instantiation

The second instantiation technique is known as direct entity instantiation.

Using this method we can directly connect the entity in a new design without declaring a component first.

The code snippet below shows how we use direct entity instantiation in VHDL.

As with the component instantiation technique, <instance_name> must be unique for each instantiation in an architecture.

There are two extra requirements for this type of instantiation. We must explicitly state the name of both the library and the architecture which we want to use. This is shown in the example above by the <library_name> and <architecture_name> labels.

Once the component is instantiated within a VHDL architecture, we use a port map to connect signals to the ports. We use the VHDL port map in the same way for both direct entity and component instantiation.

Which types can not be used with the VHDL logical operators?

Scalar types such as integer and real.

Write the code for a 4 input NAND gate

We can use two different types of statement to model multiplexors in VHDL, what are they?

The with select statement and the when else statement

Write the code for an 8 input multiplexor using both types of statement

Write the code to instantiate a two input AND component using both direct entity and component instantiation. Assume that the AND gate is compiled in the work library and the architecture is named rtl.

Leave a Reply Cancel reply

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Table of Contents

Sign up free for exclusive content.

Don't Miss Out

We are about to launch exclusive video content. Sign up to hear about it first.

- Product Manual

- Release Notes

- Screencasts

- Tech Articles

Signal Assignments in VHDL: with/select, when/else and case

Sometimes, there is more than one way to do something in VHDL. OK, most of the time , you can do things in many ways in VHDL. Let’s look at the situation where you want to assign different values to a signal, based on the value of another signal.

With / Select

The most specific way to do this is with as selected signal assignment. Based on several possible values of a , you assign a value to b . No redundancy in the code here. The official name for this VHDL with/select assignment is the selected signal assignment .

When / Else Assignment

The construct of a conditional signal assignment is a little more general. For each option, you have to give a condition. This means that you could write any boolean expression as a condition, which give you more freedom than equality checking. While this construct would give you more freedom, there is a bit more redundancy too. We had to write the equality check ( a = ) on every line. If you use a signal with a long name, this will make your code bulkier. Also, the separator that’s used in the selected signal assignment was a comma. In the conditional signal assignment, you need the else keyword. More code for the same functionality. Official name for this VHDL when/else assignment is the conditional signal assignment

Combinational Process with Case Statement

The most generally usable construct is a process. Inside this process, you can write a case statement, or a cascade of if statements. There is even more redundancy here. You the skeleton code for a process (begin, end) and the sensitivity list. That’s not a big effort, but while I was drafting this, I had put b in the sensitivity list instead of a . Easy to make a small misstake. You also need to specify what happens in the other cases. Of course, you could do the same thing with a bunch of IF-statements, either consecutive or nested, but a case statement looks so much nicer.

While this last code snippet is the largest and perhaps most error-prone, it is probably also the most common. It uses two familiar and often-used constructs: the process and the case statements.

Hard to remember

The problem with the selected and conditional signal assignments is that there is no logic in their syntax. The meaning is almost identical, but the syntax is just different enough to throw you off. I know many engineers who permanenty have a copy of the Doulos Golden Reference Guide to VHDL lying on their desks. Which is good for Doulos, because their name gets mentioned all the time. But most people just memorize one way of getting the job done and stick with it.

- VHDL Pragmas (blog post)

- Records in VHDL: Initialization and Constraining unconstrained fields (blog post)

- Finite State Machine (FSM) encoding in VHDL: binary, one-hot, and others (blog post)

- "Use" and "Library" in VHDL (blog post)

- The scope of VHDL use clauses and VHDL library clauses (blog post)

Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL by

Get full access to Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL and 60K+ other titles, with a free 10-day trial of O'Reilly.

There are also live events, courses curated by job role, and more.

4.9 VHDL SIGNAL AND GENERATE STATEMENTS

4.9.1 signal statement.

Signal is a VHDL keyword. It declares a signal of specified data type. A signal declaration is used to represent internal signals within an architecture declaration.

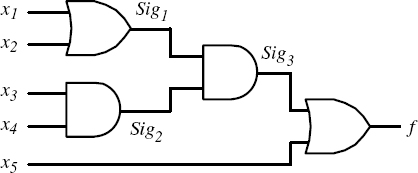

Figure 4.20 Logic Circuit with Internal Signals

Unlike entity ports, internal signals do not have a direction. Signal assignment statements execute only when the associated signals (appearing on the right-hand side of the assignment statement) change values. In VHDL, the order of concurrent statements in VHDL code does not affect the order in which the statements are executed. Signal assignments are concurrent and could execute in parallel fashion. Consider the logic circuit in Figure 4.20 where the internal signals are identified. Notice, that from the point of view of an entity declaration, the signals Sig 1 , Sig 2 , and Sig 3 are internal signals. They are neither input ports nor output ports, and therefore do not have a direction.

The VHDL program in Figure 4.21 implements the logic circuit in Figure 4.20 . The entity declaration is similar to that in the VHDL program of Figure 4.6 . The architecture declaration has been modified to include the internal signals. The logic function of the circuit is described in an indirect way using the internal signals. Both VHDL implementations ( Figures 4.6 and 4.21 ) have the same logic function and should yield the same ...

Get Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL now with the O’Reilly learning platform.

O’Reilly members experience books, live events, courses curated by job role, and more from O’Reilly and nearly 200 top publishers.

Don’t leave empty-handed

Get Mark Richards’s Software Architecture Patterns ebook to better understand how to design components—and how they should interact.

It’s yours, free.

Check it out now on O’Reilly

Dive in for free with a 10-day trial of the O’Reilly learning platform—then explore all the other resources our members count on to build skills and solve problems every day.

VHDL Concurrent Conditional Assignment

The Conditional Signal Assignment statement is concurrent because it is assigned in the concurrent section of the architecture. It is possible to implement the same code in a sequential version, as we will see next.

The conditional signal assignment statement is a process that assigns values to a signal.

It is a concurrent statement; this means that you must use it only in concurrent code sections.

The statement that performs the same operation in a sequential environment is the “ if ” statement.

The syntax for a conditional signal assignment statement is:

This is a simple example of a two-way mux as reported here:

The output “ a ” is equal to “ b ” when the selector “ c ” is “1” else is equal to “ d ”

Concurrent Conditional Signal Assignment Example 1

This example extends the previous one. This is a 4-way mux, implemented as concurrent code.

The architecture declarative section is empty. As you can notice, we don’t care about how the mux is implemented.

In this moment we don’t’ talk about logic gate, and or nand ect, we are describing the behavior of circuit using a high level description.

A graphical representation can be this one.

It is up to the synthesizer to implement the best architecture on the selected technology in terms of logic gates. In fact if you are using FPGA the synthesizer will use LUT to map the VHDL functions, if you are implementing an ASIC the synthesized logic will depend on differ technology and will be implemented using, for instance, NAND, OR, NOR gate, depending on the technology.

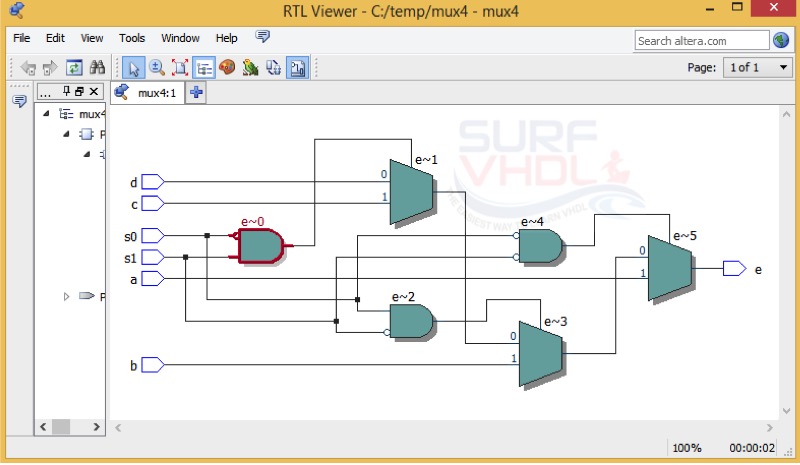

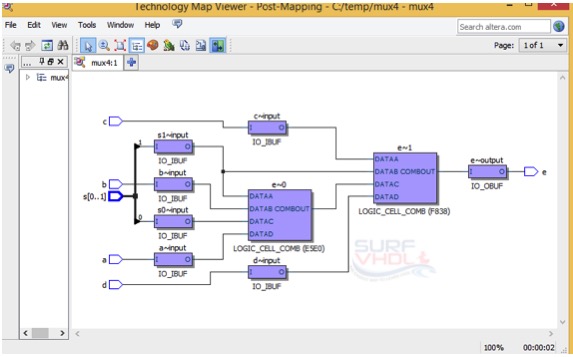

Running the RTL compiler on Altera Quartus II , this is the output of the RTL viewer, if we try to layout this mux4 .

As clear, the RTL translation is implemented in terms of AND gate and 2-way mux. The output “ e ” is generated by cascading 3 two-way mux.

This is the output of the Altera MAP viewer selecting Cyclone IV FPGA technology. Our mux4 is implemented using LOGIC_COMB_CELL Look Up Table present in the Cyclone IV FPGA . This example should clarify the meaning of “technology dependent”.

Concurrent Conditional Signal Assignment Example 2

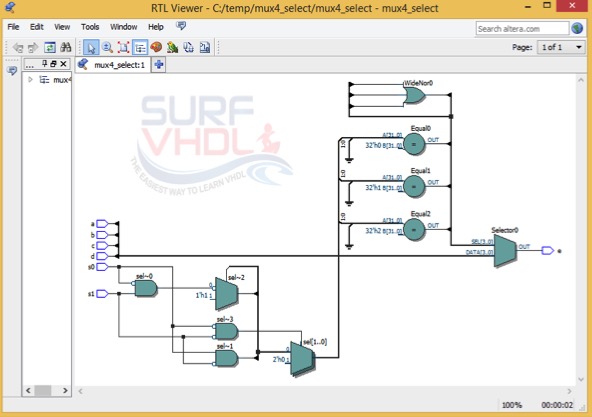

This example is the same 4-way mux as the previous one, in which we used a different syntax to implement the selector. In this case, we have introduced the statement “with select”.

In the architecture declarative section, we declared a signal “ sel ” of type integer used to address the mux. The signal “ sel ” is coded as binary to integer.

The statement “ with select ” allows compacting the syntax of the mux code. Note the introduction of the “ other ” keyword. It is necessary because the mux assignment cover only 3 of the 2^32 possible integer values. If we try to layout the code, it is interesting to see how RTL viewer interprets the VHDL code:

This case is different from the previous one. We can notice that the VHDL relative to the signal sel is decoded in order to implement mux selection and that the output mux is implemented as 4-way mux. So the RTL view of the RTL code is totally different from the previous one.

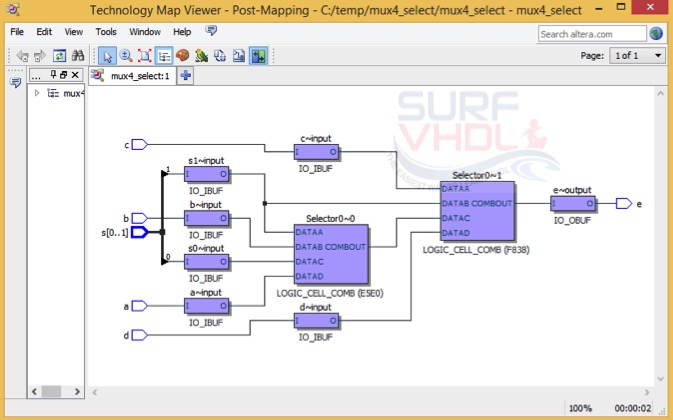

The FPGA used in this example is the same as the previous example, in fact the output of Altera MAP viewer have the same implementation of the previous RTL code as clear if we make a comparison between the two implementations.

These two examples should clarify the meaning of behavioral. We have seen two different implementations of a simple mux mapped on the same hardware :

implementation of different RTL code can generate the same hardware logic.

Of course, gaining the sensibility to write good VHDL/RTL code is only a matter of time and experience . If you will follow the course, you will find good advices in order to gain all the shortcuts useful reduce this amount of time.

Previous – Next

courses:system_design:vhdl_language_and_syntax:concurrent_statements

- Concurrent Statements

Introduction

- Concurrent statements are executed at the same time;

- independent of the order in which they appear

All statements within architectures are executed concurrently.

While it is possible to use VHDL processes as the only concurrent statement, the necessary overhead (process, begin, end, sensitivity list) lets designer look for alternatives when the sequential behavior of processes is not needed.

The signal assignment statement:

- The signal on the left side of the assignment operator ’⇐’ receives a new value whenever a signal on the right side changes.

- The new value stems from another signal or can be calculated from a number of other signals.

Conditional Signal Assignment (CSA)

- Condition is a boolean expression

- Conditions may overlap

- Equivalent of “if …, elsif …, else” constructs

The signal assignment can be extended by the specification of conditions.

The condition is appended after the new value and is introduced by the keyword ’ when ’.

VHDL'87: The keyword ’ else ’ is also strictly necessary after each condition. (as an unconditional signal assignment has to be present.)

Consequently, using VHDL'87 standard it is not possible to generate storage elements with an conditional signal assignment. Otherwise the behavior is equivalent to the if …, elsif …, else … construct that is used within processes.

VHDL’93: Conditional Signal Assignment

Vhdl rtl-synthesis standard (ieee 1076.6:2004).

6.2.1.2 Level-sensitive storage from concurrent signal assignment

“A level-sensitive storage element (=Latch) shall be modeled for a signal that is assigned in a concurrent signal assignment statement that can be mapped to a process that adheres to the rules in 6.2.1.1.”

6.2.1.1 Level-sensitive storage from process with sensitivity list

“A level-sensitive storage element (=Latch) shall be modeled for a signal (or variable) when all the following apply:

- The signal (or variable) has an explicit assignment.

- The signal (or variable) does not have an execution path with <clock_edge> as a condition.

- There are executions that do not execute an explicit assignment to the signal (or variable).”

6.4 Combinational logic

“Any process that does not contain a clock edge or wait statement shall model either combinational logic or level-sensitive sequential logic. If there is always an assignment to a variable or signal in all possible executions of the process and all variables and signals have well-defined values, then the variable or signal models combinational logic.”

➔ so if not, a Latch could be generated…

- If the variable or signal is updated before it is read in all executions of a process, then it shall model combinational logic.

- If a variable or signal is read before it is updated, then it may model combinational logic.

Conditional Signal Assignment: Example

In the example, two equivalent descriptions of a simple multiplexer are given.

Please note that all signals appearing on the right side of the signal assignment operator are entered into the process’ sensitivity list.

The unconditional else path could be replaced by an unconditional (default) signal assignment in front of the if statement.

This “default” assignments would be overwritten, if any of the conditions were true.

Selected Signal Assignment (SSA)

- Choice options must not overlap

- Single values

- Value ranges

- Selection of values (“I” means “or”)

- “when others” covers all remaining choice options ➔ is mandatory!

- Equivalent of “case …, when …” constructs

The behavior of the so called selected signal assignment is similar to the case statement.

It suffers from the same restrictions as its sequential counterpart, namely that all possible choice options have to be covered and none of the choice options may overlap with another.

Selected Signal Assignment: Example

Like with conditional signal assignments, the signal assignment operator ’⇐’ can be seen as the core of the construct.

Again, the choice options are appended after the keyword ’when’, yet the different assignment alternatives are separated by ’,’ symbols. The equivalent of the ’case EXPRESSION is’ construct from the case statement must be placed as header line in front of the actual assignment specification. The keywords have to be translated, however, to ’with EXPRESSION select’.

- Conditional signal assignment: decision based upon several signals

- Selected signal assignment: decision based upon values of an expression

- Conditional signal assignment ⇔ if …, elsif …, else …, end if

- Selected signal assignment ⇔ case …, when …, end case

All concurrent statements describe the functionality of multiplexer structures.

VHDL'87 : It is impossible to model storage elements , like flip flops with concurrent statements, only.

Consequently, the unconditional else path is necessary in conditional signal assignments.

Every concurrent signal assignment, whether conditional or selected, can be modelled with a process construct, however.

As sequentially executed code is easier comprehensible, the concurrent versions should be used as shortcut when simple functionality would be obfuscated by the process overhead, only.

- ...are only executed, when a signal changes, that is read in the statement.

- ...appear in the statement part of an architecture.

Chapters of System Design > VHDL Language and Syntax

- General Issues

- VHDL Structural Elements

- Process Execution

- Extended Data Types

- Sequential Statements

- Subprograms

- Subprogram Declaration and Overloading

VIDEO

COMMENTS

The signal assignment operator specifies a relationship between signals. In other words, the signal on the left side of the signal assignment operator is dependent upon the signals on the right side of the operator. (Source: Digital_Mclogic_Design by Bryan Mealy, Section: The Signal Assignment Operator: "<=", page 339)

The VHDL code shown below uses one of the logical operators to implement this basic circuit. and_out <= a and b; Although this code is simple, there are a couple of important concepts to consider. The first of these is the VHDL assignment operator (<=) which must be used for all signals.

The statement "Others => '0'" is a feature of the VHDL when the coder want to defined several items in an array with the same value. In your example, all item std_logic in the array are set to '0'. Another application of this statement is to set some items at a specific value and all others at a default value : cmd_r <= (0 => '1', 4 => '1',

In VHDL there are two assignment symbols: <= Assignment of Signals. := Assignment of Variables and Signal Initialization. Either of these assignment statements can be said out loud as the word "gets". So for example in the assignment: test <= input_1; You could say out loud, "The signal test gets (assigned the value from) input_1.".

1 1. Bits, Vectors, Signals, Operators, Types 1.1 Bits and Vectors in Port Bits and vectors declared in port with direction. Example: port ( a : in std_logic; -- signal comes in to port a from outside b : out std_logic; -- signal is sent out to the port b c : inout std_logic; -- bidirectional port x : in std_logic_vector(7 downto 0); -- 8-bit input vector

With / Select. The most specific way to do this is with as selected signal assignment. Based on several possible values of a, you assign a value to b. No redundancy in the code here. The official name for this VHDL with/select assignment is the selected signal assignment. with a select b <= "1000" when "00", "0100" when "01", "0010" when "10 ...

A VHDL description has two domains: a sequential domain and a concurrent domain. The sequential domain is represented by a process or subprogram that contains sequential statements. These statements are exe-cuted in the order in which they appear within the process or subprogram, as in programming languages.

The next statement is a condition that tests whether the en signal is '1'. If it is, the statements between the keywords then and end if are executed, updating the pro-cess's variables using the values on the input signals. After the conditional if state-ment, there are four signal assignment statements that cause the output signals to be

Version 1.5, please report any issues to [email protected]. Compact Summary of VHDL. This is not intended as a tutorial. This is a quick reference guide to find the statement or statement syntax you need to write VHDL code. VHDL is case insensitive, upper case letters are equivalent to lower case letters. Reserved words are in lower case by ...

A signal assignment statement updates the signal driver. The new value of the signal is updated when the ... Variables are cheaper to implement in VHDL simulation since the evaluation of drivers is not needed. They require less memory. 4. Signals communicate among concurrent statements. Ports declared in the entity are signals. Subprogram

The VHDL program in Figure 4.8 implements the 2: 1 multiplexer in Figure 4.7. The function of the multiplexer is described in the architecture of the code using selected signal assignment statements. The signal assignment statement selected begins with the reserved keyword with followed by the selection condition, which is in the input signal, s.

The outputs include a 2-bit signal (code), which is the binary code of the highest priority request and a 1-bit signal active that indicates if there is an active request. has the highest priority, i.e., when asserted, the other three requests are ignored and the code signal becomes "11". When r(3) is not asserted, the second highest request, r ...

Conditional Signal Assignment or the "When/Else" Statement. The "when/else" statement is another way to describe the concurrent signal assignments similar to those in Examples 1 and 2. Since the syntax of this type of signal assignment is quite descriptive, let's first see the VHDL code of a one-bit 4-to-1 multiplexer using the ...

1 1. Add a comment. "what is the meaning of this statement in VHDL" You show three statements but I imagine you mean the third one, the assignment statement: aIn : in STD_LOGIC; signal oSyncStages : std_logic_vector(STAGES-1 downto 0); oSyncStages <= oSyncStages(oSyncStages'high-1 downto 0) & aIn; In a clocked process, the assignment will ...

4.9 VHDL SIGNAL AND GENERATE STATEMENTS 4.9.1 Signal Statement. Signal is a VHDL keyword. It declares a signal of specified data type. A signal declaration is used to represent internal signals within an architecture declaration.. Figure 4.20 Logic Circuit with Internal Signals. Unlike entity ports, internal signals do not have a direction. Signal assignment statements execute only when the ...

Another concurrent statement is known as component instantiation. Component instantiation can be used to connect circuit elements at a very low level or most frequently at the top level of a design. VHDL written in this form is known as Structural VHDL. The instantiation statement connects a declared component to signals in the architecture.

Time in a process only advances due to stopping at a sensitivity list or due to a wait statement. And a process never has both a sensitivity list and a wait statement. Again they are different enough to warrant learning how VHDL's signals and variables work independent of how Verilog's blocking and non-blocking assignments.

Conditional signal assignment. Conditional signal assignment is a form of a concurrent signal assignment and plays the same role in architecture as the if then else construct inside processes. A signal is assigned a waveform if the Boolean condition supported after the when keyword is met. Otherwise, the next condition after the else clause is ...

The conditional signal assignment statement is a process that assigns values to a signal. It is a concurrent statement; this means that you must use it only in concurrent code sections. The statement that performs the same operation in a sequential environment is the " if " statement. The syntax for a conditional signal assignment statement is:

5. Where you are hinting at in your problem has nothing to do with concurrent assignments or sequential statements. It has more to do with the difference between if and case. Before we get to that first lets understand a few equivalents. The concurrent conditional assignment: Y <= A when ASel = '1' else B when BSel = '1' else C ;

VHDL RTL-Synthesis Standard (IEEE 1076.6:2004) 6.2.1.2 Level-sensitive storage from concurrent signal assignment. "A level-sensitive storage element (=Latch) shall be modeled for a signal that is assigned in a concurrent signal assignment statement that can be mapped to a process that adheres to the rules in 6.2.1.1.".