Verilog assign statement

Hardware schematic.

Signals of type wire or a similar wire like data type requires the continuous assignment of a value. For example, consider an electrical wire used to connect pieces on a breadboard. As long as the +5V battery is applied to one end of the wire, the component connected to the other end of the wire will get the required voltage.

In Verilog, this concept is realized by the assign statement where any wire or other similar wire like data-types can be driven continuously with a value. The value can either be a constant or an expression comprising of a group of signals.

Assign Syntax

The assignment syntax starts with the keyword assign followed by the signal name which can be either a single signal or a concatenation of different signal nets. The drive strength and delay are optional and are mostly used for dataflow modeling than synthesizing into real hardware. The expression or signal on the right hand side is evaluated and assigned to the net or expression of nets on the left hand side.

Delay values are useful for specifying delays for gates and are used to model timing behavior in real hardware because the value dictates when the net should be assigned with the evaluated value.

- LHS should always be a scalar or vector net or a concatenation of scalar or vector nets and never a scalar or vector register.

- RHS can contain scalar or vector registers and function calls.

- Whenever any operand on the RHS changes in value, LHS will be updated with the new value.

- assign statements are also called continuous assignments and are always active

In the following example, a net called out is driven continuously by an expression of signals. i1 and i2 with the logical AND & form the expression.

If the wires are instead converted into ports and synthesized, we will get an RTL schematic like the one shown below after synthesis.

Continuous assignment statement can be used to represent combinational gates in Verilog.

The module shown below takes two inputs and uses an assign statement to drive the output z using part-select and multiple bit concatenations. Treat each case as the only code in the module, else many assign statements on the same signal will definitely make the output become X.

Assign reg variables

It is illegal to drive or assign reg type variables with an assign statement. This is because a reg variable is capable of storing data and does not require to be driven continuously. reg signals can only be driven in procedural blocks like initial and always .

Implicit Continuous Assignment

When an assign statement is used to assign the given net with some value, it is called explicit assignment. Verilog also allows an assignment to be done when the net is declared and is called implicit assignment.

Combinational Logic Design

Consider the following digital circuit made from combinational gates and the corresponding Verilog code.

Combinational logic requires the inputs to be continuously driven to maintain the output unlike sequential elements like flip flops where the value is captured and stored at the edge of a clock. So an assign statement fits the purpose the well because the output o is updated whenever any of the inputs on the right hand side change.

After design elaboration and synthesis, we do get to see a combinational circuit that would behave the same way as modeled by the assign statement.

See that the signal o becomes 1 whenever the combinational expression on the RHS becomes true. Similarly o becomes 0 when RHS is false. Output o is X from 0ns to 10ns because inputs are X during the same time.

Click here for a slideshow with simulation example !

Assign Statement In Verilog

- You can use assign statement inside of module.

- You can use assign statement to output port and any wire declared inside the module

Examples of assign statement

In above example, y is output port and we are assigning this output port to a and b. It will create a and gate where a and b are inputs and y is output

In above example, we've descrived a NAND gate. We can use one statemetn but for better understanding we've use two statement to illustrate how we can use assign statement to both wire and output port. wire w is assign with a AND b, and output y is assigned not of wire w. This creates a NAND gate in verilog HDL.

In above example, we have described a full-adder using assign statement. Note that we can write complete boolean equation using assign statement

We can also use Verilog operators using assign statement. Below is the example of full-adder using assign statement and Verilog operator

In above example, we are using + operator, which addition operator in Verilog. We are assigning output sum and carry with addition of a, b and cin.

Click like if you found this useful

Add Comment

This policy contains information about your privacy. By posting, you are declaring that you understand this policy:

- Your name, rating, website address, town, country, state and comment will be publicly displayed if entered.

- Your IP address (not displayed)

- The time/date of your submission (displayed)

- Administrative purposes, should a need to contact you arise.

- To inform you of new comments, should you subscribe to receive notifications.

- A cookie may be set on your computer. This is used to remember your inputs. It will expire by itself.

This policy is subject to change at any time and without notice.

These terms and conditions contain rules about posting comments. By submitting a comment, you are declaring that you agree with these rules:

- Although the administrator will attempt to moderate comments, it is impossible for every comment to have been moderated at any given time.

- You acknowledge that all comments express the views and opinions of the original author and not those of the administrator.

- You agree not to post any material which is knowingly false, obscene, hateful, threatening, harassing or invasive of a person's privacy.

- The administrator has the right to edit, move or remove any comment for any reason and without notice.

Failure to comply with these rules may result in being banned from submitting further comments.

These terms and conditions are subject to change at any time and without notice.

- Verilog assign statement

Table of Contents

- Lexical Tokens

- Integer Datatype

- Real Datatype

- Time Datatype

- real time Datatype

- string Data Type

- event Data type

- Scalar and Vector

- Verilog Abstraction Layer

- Verilog Array

- Verilog Memory array

- Verilog Operators

- Behavioral Modelling

- always block

- Initial block

- Procedural assignment

- Verilog generate block

Assign statement

The assign statement in Verilog is used to continue assigning a value to a wire data type. In data flow modeling , it is also used. Concurrent assignment statements like this one are commonly used to show combinational logic. The assign statement explains how an original statement and a target are related, declaring that the value of the target i.e. “sample” should always match the value of the original statement.

The syntax of the assign statement is as follows:

Here, sample is the wire to which the value will be continuously assigned , and original_expression is the expression whose value will be assigned to the sample. The expression can be a combination of constants, signals, operators, and other wires.

Let us consider an easy example to show how to use the assign statement:

In the above example, the module and_gate accepts the signals x and y as inputs and outputs the signal F . The assign statement represents a logical AND operation between inputs x and y by constantly assigning the value of x & y to the output F .

Rules of assign statement:

The following guidelines must be observed when using an assign statement:

1. LHS should never be a scalar or vector register, but rather a scalar or vector net, or a combination of both.

2. scalar or vector registers, as well as function calls, can be found in RHS.

3. The LHS will be updated with any changes to the values of any operands on the RHS.

4. Continuous assignments are another name for assign statements.

The assign statement only operates with wire data types , and this must be remembered .

To represent sequential behavior for registers ( such as reg ), procedural assignments (such as always blocks) must be used. Within Verilog modules, procedural assignments provide the description of a clock or sequential logic. Top of Form

Privacy Policy - Terms and Conditions

- The Verilog-AMS Language

- Continuous Assigns

Continuous Assigns

A module may have any number of continuous assign statements. Continuous assign statements are used to drive values on to wires. For example:

This is referred to as a continuous assign because the wire on the left-hand side of the assignment operator is continuously driven with the value of the expression on the right hand side. The target of the assign statement must be a wire. The continuous assign statement is not a procedural statement and so must be used at the module level; it cannot be placed in an initial or always process.

You can add delay to a continuous assign statement as follows:

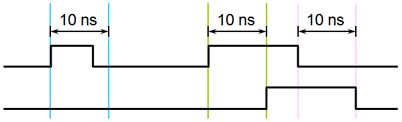

In this case, the value of a changes 10 units of time after the expression b & c changes. Continuous assign statement implement inertial delay, meaning that continuous assign statements swallow glitches. This is illustrated below with the assumption that the unit of time is 1ns.

It is possible to specify up to three delay values on a continuous assignment:

When you specify more than one:

The first delay refers to the transition to the 1 value (rise delay).

The second delay refers to the transition to the 0 value (fall delay).

The third delay refers to the transition to the high-impedance value.

When a value changes to the unknown (x) value, the delay is the smallest of the delays specified.

If only two delays are specified, then the delay to high-impedance is the smallest of the two values specified.

Stack Exchange Network

Stack Exchange network consists of 183 Q&A communities including Stack Overflow , the largest, most trusted online community for developers to learn, share their knowledge, and build their careers.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Difference between blocking and nonblocking assignment Verilog

I was reading this page http://www.asic-world.com/verilog/verilog_one_day3.html when I came across the following:

We normally have to reset flip-flops, thus every time the clock makes the transition from 0 to 1 (posedge), we check if reset is asserted (synchronous reset), then we go on with normal logic. If we look closely we see that in the case of combinational logic we had "=" for assignment, and for the sequential block we had the "<=" operator. Well, "=" is blocking assignment and "<=" is nonblocking assignment. "=" executes code sequentially inside a begin / end, whereas nonblocking "<=" executes in parallel.

I was fairly sure that nonblocking assignments were sequential while blocking assignments were parallel. After all, you can make blocking assignments with assign statements outside of always blocks, and those all run in parallel. Is this a mistake, or is the behavior different inside an always block? And, if the behavior IS different inside an always block, can nonblocking assignments be made outside an always block?

3 Answers 3

was fairly sure that nonblocking assignments were sequential while blocking assignments were parallel.

Blocking assignment executes "in series" because a blocking assignment blocks execution of the next statement until it completes. Therefore the results of the next statement may depend on the first one being completed.

Non-blocking assignment executes in parallel because it describes assignments that all occur at the same time. The result of a statement on the 2nd line will not depend on the results of the statement on the 1st line. Instead, the 2nd line will execute as if the 1st line had not happened yet.

- \$\begingroup\$ So what about assign statements? Are they just in a whole class of their own? \$\endgroup\$ – Void Star Commented Nov 24, 2013 at 4:25

- 6 \$\begingroup\$ Yes, assign statements occur outside of always blocks and are generally used to describe to combinatorial (un-latched) logic (while always blocks, with some exceptions, describe sequential logic). AFAIK, assign statements always execute "in parallel" whenever their LHS has a value change. \$\endgroup\$ – The Photon Commented Nov 24, 2013 at 4:28

- \$\begingroup\$ Okay... I'm starting to get the impression that Verilog just isn't the most elegantly designed language. This is gonna be like learning C was. \$\endgroup\$ – Void Star Commented Nov 24, 2013 at 5:30

- 2 \$\begingroup\$ Verilog was designed to "describe" hardware that already exists. Using it as a language to design (synthesize) hardware is a hack. \$\endgroup\$ – The Photon Commented Nov 24, 2013 at 6:02

- 6 \$\begingroup\$ if Verilog "like learning C" is a problem, take a look at VHDL. Some people have fairly strong preferences for one or the other. To some, VHDL is just too verbose. To me, it's much better thought out. (signal/variable assignment semantics are much clearer than blocking/non for example). stackoverflow.com/questions/13954193/… and sigasi.com/content/vhdls-crown-jewel You may prefer it or hate it. But it's worth a look. \$\endgroup\$ – user16324 Commented Nov 24, 2013 at 10:20

Assign statements are neither "blocking" or "nonblocking", they are "continuous". The output of an assign statement is always equal to the specified function of it's inputs. "blocking" and "nonblocking" assignments only exist within always blocks.

A blocking assignment takes affect immediately it is processed. A nonblocking assignment takes place at the end of processing the current "time delta".

always blocks can be used to model either combinatorial or sequential logic (systemverilog has always_comb and always_ff to make this explicit). When modeling combinatorial logic it's usually more efficient to use = but it typically doesn't really matter.

When modelling sequential logic (e.g. always @(posedge clk) ) you normally use nonblocking assingments. This allows you to deterime the "state after the clock edge" in terms of "the state before the clock edge".

It is sometimes useful to use blocking assignments in sequential always blocks as "variables". If you do this then there are two key rules to bear in mind.

- Do not access a reg that is set with blocking assignments inside a sequential always block from outside the always block it is assigned in.

- Do not mix blocking and nonblocking assignments to the same reg.

Breaking these rules is likely to result in synthesis failures and/or behaviour differences between simulation and synthesis.

- \$\begingroup\$ ""Do not access a reg that is set with blocking assignments inside a sequential always block from outside the always block it is assigned in."" Can you please explain it? \$\endgroup\$ – user125575 Commented Oct 4, 2016 at 6:44

- 2 \$\begingroup\$ Different sequential always blocks do not have a defined order. So reading a "reg" set with a blocking assingment in one always block from another always block will lead to unpredicable behaviour. \$\endgroup\$ – Peter Green Commented Oct 4, 2016 at 15:23

- \$\begingroup\$ And even if it appears to work in simulation, a synthesis tool should look at that and say "nope". I use local regs for those intermediate vars, and make sure that they are always assigned to on every clock before being read, so that no 'storage' is implied. \$\endgroup\$ – greggo Commented Mar 30, 2017 at 11:57

- \$\begingroup\$ IIRC at least in quartus it is only considered a warning not an error. \$\endgroup\$ – Peter Green Commented Mar 30, 2017 at 11:59

- \$\begingroup\$ You should not be using nonblocking assignment in combinational logic, it can lock up the simulation. For more details, refer this answer: electronics.stackexchange.com/a/506047/238188 \$\endgroup\$ – Shashank V M Commented Oct 5, 2020 at 14:55

The term Blocking assignment confuses people because the word blocking would seem to suggest time-sequential logic. But in synthesized logic it does not mean this , because everything operates in parallel .

Perhaps a less confusing term would be immediate assignment , which would still differentiate the intermediate results of combinational logic from the inputs to non-transparent memory elements (for example clocked registers), which can have delayed assignment .

From a legalistic standpoint, it all works out very nicely. You can, in fact, consider the = to be a blocking (time-sequential) operation even within always_comb sequences. However, the distinction between time-sequential and parallel makes absolutely no difference in this case because the always_comb block is defined to repeat until the instruction sequence converges on a stable state -- which is exactly what the hardware circuitry will do (if it meets the timing requirements).

The synthesizable subset of Verilog (and especially SystemVerilog) is extremely simple and easy to use -- once you know the necessary idioms. You just have to get past the clever use of terminology associated with the so-called behavioral elements in the language.

- \$\begingroup\$ In behavioral coding styles ( as compared to RTL ), the distinction between blocking and non-blocking can be relevant. In some cases, the synthesis tool may be able to infer functionally equivalent RTL from behavioral component designs. \$\endgroup\$ – Brent Bradburn Commented Jul 21, 2015 at 17:28

- \$\begingroup\$ Of course the procedural mode of SystemVerilog, applicable especially to initial statements within program blocks, uses (time-sequential) blocking assignment exclusively. This is useful for testbench design, but generally not for RTL specification. \$\endgroup\$ – Brent Bradburn Commented Dec 18, 2015 at 18:58

Your Answer

Sign up or log in, post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged verilog or ask your own question .

- Featured on Meta

- Upcoming sign-up experiments related to tags

Hot Network Questions

- Is there an easy way to batch the change of StyleSheet in 120 Notebooks

- Cancellation of the Deutschlandticket

- How are "pursed" and "rounded" synonymous?

- Why was the animal "Wolf" used in the title "The Wolf of Wall Street (2013)"?

- Why do we care if the likelihood function is tractable?

- Different Bekenstein bound equations – what’s the difference?

- Fantasy TV series with a male protagonist who uses a bow and arrows and has a hawk/falcon/eagle type bird companion

- Old book about a man who finds an abandoned house with a portal to another world

- How to produce this table: Probability datatable with multirow

- Is automorphism on a compact group necessarily homeomorphism?How about N-dimensional torus?

- What does ‘a grade-hog’ mean?

- How will the ISS be decommissioned?

- What could explain that small planes near an airport are perceived as harassing homeowners?

- What is the original source of this Sigurimi logo?

- Why Owasp-crs does not allow Content-Type: application/x-www-form-urlencoded

- Can I tell a MILP solver to prefer solutions with fewer fractions?

- Less ridiculous way to prove that an Ascii character compares equal with itself in Coq

- What kind of sequence is between an arithmetic and a geometric sequence?

- Is it possible to complete a Phd on your own?

- Is there any other reason to stockpile minerals aside preparing for war?

- Correlation for Small Dataset?

- DSP Puzzle: Advanced Signal Forensics

- How to Pick Out Strings of a Specified Length

- Algorithm to evaluate "connectedness" of a binary matrix

- Interview Q

IMAGES

VIDEO

COMMENTS

The LHS of an assign statement cannot be a bit-select, part-select or an array reference but can be a variable or a concatenation of variables. reg q; initial begin assign q = 0; #10 deassign q; end force release. These are similar to the assign - deassign statements but can also be applied to nets and variables. The LHS can be a bit-select of ...

Assignment. A assignment evaluates the expression on its right hand side and then immediately assigns the value to the variable on its left hand side: a = b + c; The target (left side) of an analog assignment statement may only be a integer or real variable. It may not be signal or a wire.

Verilog assign statement. Signals of type wire or a similar wire like data type requires the continuous assignment of a value. For example, consider an electrical wire used to connect pieces on a breadboard. As long as the +5V battery is applied to one end of the wire, the component connected to the other end of the wire will get the required ...

Blocking Assignment. A blocking assignment evaluates the expression on its right hand side and then immediately assigns the value to the variable on its left hand side: a = b + c; It is also possible to add delay to a blocking assignment. For example: a = #10 b + c; In this case, the expression on the right hand side is evaluated and the value ...

For example, in this code, when you're using a non-blocking assignment, its action won't be registered until the next clock cycle. This means that the order of the assignments is irrelevant and will produce the same result. The other assignment operator, '=', is referred to as a blocking assignment. When '=' assignment is used, for the purposes ...

assign keyword is used to assign ouput port or wire some digital logic. This keyword is the part of dataflow modeling in Verilog. In this post, we will see how to use this keyword in your Verilog code. You can use assign statement inside of module. You can use assign statement to output port and any wire declared inside the module.

The assign statement in Verilog is used to continue assigning a value to a wire data type. In data flow modeling, it is also used. Concurrent assignment statements like this one are commonly used to show combinational logic. The assign statement explains how an original statement and a target are related, declaring that the value of the target ...

Continuous assign statements are used to drive values on to wires. For example: assign a = b & c; This is referred to as a continuous assign because the wire on the left-hand side of the assignment operator is continuously driven with the value of the expression on the right hand side. The target of the assign statement must be a wire.

The explicit assignment require two statements: one to declare the net (see Net data type), and one to continuously assign a value to it. Continuous assignments are not the same as procedural ...

This Verilog-A Hardware Description Language (HDL) language reference manual defines a behavioral language for analog systems. Verilog-A HDL is derived from the IEEE 1364 Verilog HDL specification. This document is intended to cover the definition and semantics of Verilog-A HDL as proposed by Open Verilog International (OVI).

The output of an assign statement is always equal to the specified function of it's inputs. "blocking" and "nonblocking" assignments only exist within always blocks. A blocking assignment takes affect immediately it is processed. A nonblocking assignment takes place at the end of processing the current "time delta".

Microsoft PowerPoint - L03_Verilog v2.pptx. Intro to Verilog. • Wires - theory vs reality (Lab1) • Hardware Description Languages. • Verilog -- structural: modules, instances -- dataflow: continuous assignment -- sequential behavior: always blocks -- pitfalls -- other useful features. Reminder: Lab #1 due by 9pm tonight.

The assign statement serves as a conditional block like an if statement you are probably used to in popular programming languages such as C or C++. The assign operator works as such: Assign my value to other values based upon if certain conditions are true. The above assign operator works as follows: If val == 2'b00, assign x to the value of a.

And these are the two types. 1. Assign deassign: It will override all procedural assignments to a variable and deactivate it using the same signal with deassign. The value of the variable will remain the same until the variable gets a new value through a procedural or procedural continuous assignment.

Verilog assign statement result check. 2. Multiple conditions in If statement Verilog. 0. Signal assignments from multiple if statements. 1. Conditional Assignment in Verilog. Hot Network Questions Are there substantive differences between the different approaches to "size issues" in category theory?

`define foo 3 `define \bar 4 assign w1 = `foo ; assign w2 = `\foo ; assign w3 = `bar ; assign w4 = '\bar ; In Section 19.3.1, we are told that all compiler directives shall be considered predefined macro names, and it shall be illegal to redefine a compiler directive as a macro name. And Verilog-XL seems to rightfully complain about things like:

Course Catalog. Class Schedule; Course Catalog; Undergraduate; Graduate; Copyright © 2024-25, UC Regents; all rights reserved.Accessibility

It is called procedural continuous assignment.It is the use of an assign or force (and their corresponding counterparts deassign and release) within procedural block.A new continuous assignment process is created when the line is reached in the procedural block. assign can be applied to register types such as reg, integer, and real.force can be applied to registers and nets (i.e. wires).

You need to remove the reg[3:0] in the initial block so that the assignment get applied the the intended counter. But it will still not work because you declared counter as an inferred wire type and always / initial blocks cannot assign wires. counter was declared as an output of a 4-bit inferred wire ( output [3:0] counter is synonyms to ...

The assignments and testbench is in verilog language with assertions based tests. Is there any tool or methodology which I can use to grade all the assignments in one go? Can I run a utility or piece of code on github to do this? automation; verilog; assertion; Share. Improve this question.